無論設計航太和國防系統、測試和測量設備,或是汽車光達類比前端 (AFE),使用現代高速資料轉換器的硬體設計人員皆面臨高頻率輸入、輸出、時脈速率和數位介面的嚴峻挑戰。問題可能包括連接現場可編程邏輯閘陣列 (FPGA)、確認初次設計成果,或確認在建構系統之前如何進行系統的最佳建模。

本文將深入探討其中的每項挑戰。

快速系統開發

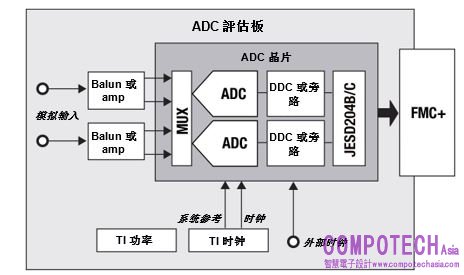

在開始新的硬體設計之前,工程師經常藉由自己的測試工作臺評估最重要的晶片。在獲得執行一般評估板所需的設備之後,元件評估通常會以理想狀態下的電源和訊號來源進行。TI 通常提供板載電源和時脈,以便使用最少的測試工作臺設備以及更符合實際情況的電源和訊號來源開始執行一般評估板,如圖 1 所示。

圖 1:一般 ADC 評估板

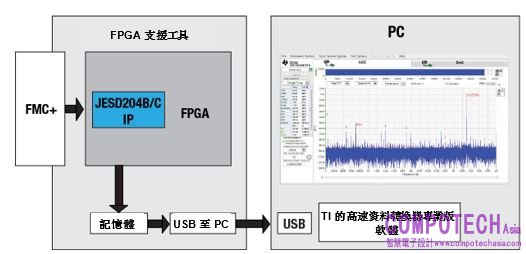

驗證效能後,即可使用更完整的評估板的示意圖和配置做為子系統該部份的參考設計。我們的資料擷取和模式產生工具支援 CMOS、LVDS 和 JESD204,並提供操作所需的軟體。使用高速資料轉換器的評估板使用者指南,可以在10 分鐘以內啟動並執行大多數評估板。見圖 2。

圖 2:TI 資料擷取和模式產生硬體與軟體

由於系統愈來愈複雜,可能會需要評估更廣泛的應用實例,評估板剛好可以發揮作用。如果評估需求變得複雜,則可以使用 Python、Matlab、Labview 或 C ++ 軟體透過評估模組、擷取卡解決方案和測試工作臺設備直接與裝置進行通訊。 TI的支援板包括 LVDS/CMOS 的 TSW1400EVM 或支援 JESD204B 串聯器-解串器 (SerDes) 通訊協定裝置的 TSW14J56EVM,如圖 3 所示。

圖 3:TI 的 TSW14J56EVM,用於 JESD204B 資料擷取或模式產生

TI 也對於單一 PC 的多評估模組原型支援完整系統層級模型試驗。例如,將 Xilinx FPGA 開發套件 (例如 KCU105 或 VCU118) 連接到多個類比轉數位轉換器 (ADC) 或類比轉數位轉換器 (DAC),可以同時測試發射和接收通道。探索TI的 JESD204 快速設計 IP,藉以簡化 FPGA 整合並縮短整體開發時間。

FPGA 連線功能以及 JESD204B 與 JESD204C

另一項可能需要解決的最大問題是如何在 FPGA 中收發資料。雖然 LVDS 和 CMOS 是簡單的介面,但這些介面對於裝置的每個針腳支援的速度相當有限。隨著更新的高速資料轉換器更加廣泛支援小於 1 GSPS 的輸入或輸出速率,這些介面很容易耗盡資源,或者並不容易用於設計。

電子裝置工業委員會(JEDEC)為微電子產業建立了開放標準並推出 JESD204,藉由支援超過 12.5 Gbps 的差分對通道速率來解決這類問題。雖然 JESD204 盡可能減少針腳數,但這確實對並行資料進行編碼和序列化或進行反序列化和解碼而增加介面的複雜度。

直到今日,我們必須主要仰賴 JESD204 智慧財產權 (IP) 區塊和 FPGA 供應商提供的支援。這些 IP 區塊雖然可以正常運作,但它也支援任何裝置的任何客製配置。這表示難以針對特定應用實例學習與配置這些區塊,我們必須耗費心力設計自己的 IP,或者採用第三方 IP 供應商的 IP。但是,如果出現問題,第三方 IP 將會需要實施這些措施的協助和支援。

TI JESD204 快速設計 IP 可針對 FPGA 平台、資料轉換器和 JESD204 模式進行預先配置和優化。我們的 IP 僅需較少的 FPGA 資源,同時並可針對各類特定用途進行自訂。另一項優點是僅需要數小時或數天即可實現 JESD204 連結,不需要數週或數月。

裝置模型

由於直接射頻 (RF) 採樣和極快速 SerDes 與高速資料轉換器的結合愈來愈普遍,對 RF 和訊號完整性進行建模的能力逐漸成為初次設計的成功必要條件。長期以來,大多數供應商僅針對 S 參數模型中的 ADC 提供輸入阻抗資訊,然而 TI 的 ADC12DJ3200、ADC12DJ5200RF 和 ADC12QJ1600-Q1 高頻率輸入裝置,針對高達 8 GHz 的採樣頻率, 也具有 S 參數模型,包括阻抗和頻率回應資訊。

使用該項新模型,即可模擬預期的裝置行為並優化阻抗配對。TI 的策略為針對支援極高輸入和輸出頻率的裝置提供這些模型,然而阻抗配對和達成所需的頻率回應則更具挑戰性。

對於資料轉換器的數位介面,輸入/輸出緩衝區資訊規格 (IBIS) 為常用的模型,可提供 CMOS 和 LVDS 針腳的實體層資訊,以及 DC 和 AC 類型的行為。對於使用高速 JESD204 SerDes 的大多數新型資料轉換器,這些模型已改進為 IBIS 演算法建模介面 (AMI),有助於等化效果和前置或後置強化的資訊。IBIS-AMI 提供所需的建模功能,讓客戶第一次就設計出正確的電路板,同時達到良好的位元錯誤率、訊號完整性和穩定的資料連結。圖 4 顯示 RF (綠色) 和數位介面 (藍色) 模型。

圖4:介面建模

結論

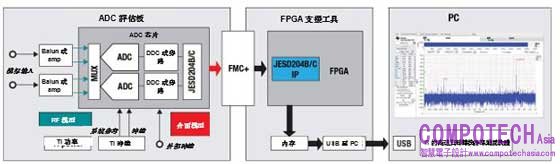

無論您已使用高速資料轉換器進行設計有一段時間,或是尚未熟悉高速設計的新手,TI 皆能為您提供簡化的程序來進行設計。我們整合完整的開發環境,將這些工作變得更輕鬆容易,如圖 5 所示。

無論您已使用高速資料轉換器進行設計有一段時間,或是尚未熟悉高速設計的新手,TI 皆能為您提供簡化的程序來進行設計。我們整合完整的開發環境,將這些工作變得更輕鬆容易,如圖 5 所示。

藉由可輕鬆實現的FPGA 整合現成 IP,精確的 RF 系統模型,以及市場上最強大而且靈活、可擴充且可自動化的一整套評估模組,即可縮短數月的韌體開發時間、縮短高成本的設計週期,並加快從概念到原型的高速設計。

圖 5:一般高速類比轉數位轉換器 (ADC) 評估環境

其他資源

• 請參考TI高速資料轉換器專業軟體以評估高速資料轉換器或 AFE 平台

• 請參考應用報告:從 JESD204B 升級到 JESD204C 時的系統設計考量

• 請參考技術文章:S 參數到底是什麼?

• 請觀看系列影片:高速類比轉數位轉換器 (ADC) 基礎知識

• 請參考TI高速資料轉換器專業軟體以評估高速資料轉換器或 AFE 平台

• 請參考應用報告:從 JESD204B 升級到 JESD204C 時的系統設計考量

• 請參考技術文章:S 參數到底是什麼?

• 請觀看系列影片:高速類比轉數位轉換器 (ADC) 基礎知識

關於德州儀器(TI)

德州儀器(納斯達克股票代碼:TXN)為位居世界領導地位的全球半導體公司,致力於設計、製造、測試以及銷售類比和嵌入式半導體晶片,為工業、汽車、個人電子、通訊設備和企業系統等市場服務。打造更美好的世界是我們的願景,為此,我們以半導體技術為基礎,致力於創造更輕巧、更高效、更可靠及更具成本效益的產品解決方案,使半導體更加普及地被應用於各式電子產品中。推動半導體技術持續更上一層樓,是我們數十年來始終如一的信念。更多詳情,敬請瀏覽TI.com。

德州儀器(納斯達克股票代碼:TXN)為位居世界領導地位的全球半導體公司,致力於設計、製造、測試以及銷售類比和嵌入式半導體晶片,為工業、汽車、個人電子、通訊設備和企業系統等市場服務。打造更美好的世界是我們的願景,為此,我們以半導體技術為基礎,致力於創造更輕巧、更高效、更可靠及更具成本效益的產品解決方案,使半導體更加普及地被應用於各式電子產品中。推動半導體技術持續更上一層樓,是我們數十年來始終如一的信念。更多詳情,敬請瀏覽TI.com。