近幾年常聽聞:將電子設計自動化 (EDA) 往下延伸至「系統層級」有多重要、高階合成 (HLS) 有多方便、加入人工智慧 (AI)/機器學習 (Machine Learning, ML) 功能有多聰明……。究竟,真相為何?它們之間又有怎樣的連動?

Mentor IC EDA部門執行副總裁 Joseph Sawicki 表示,半導體正隱約透露一絲悲觀氣息:創投 (VC) 支出明顯下降、公司寧用合併取代創新……,而AI/ML 極可能成為驅動另一次半導體成長循環的救世主,且此波週期將數以十年計,半導體廠商應抓住 AI 所帶來的無限可能、發揮優勢,實現市場潛力,預估能從技術堆疊中獲取 40~50 % 價值——相較於手機領域的 20%,至少倍數起跳。數據爆炸將引導 5G 等高頻寬架構發展,包括車聯網在內的工商行為及消費性物聯網 (IoT) 應用,將為 AI 訓練提供糧食,確保有效處理並使用所有數據。

照片人物:Mentor IC EDA部門執行副總裁 Joseph Sawicki

邊緣裝置主導,AI / ML 晶片市場將以三位數成長

由於數據爆炸,截至 2030 年,高速數據通訊將呈現指數級增長,而看似對立、卻相互影響的兩股勢力正在推進 AI:一是強化資料中心的演算能力,二是將更多處理工作推至邊緣 (Edge)。在邊緣裝置主導下,AI/ML 晶片市場將以三位數成長,力道將超越邊緣設備本身;但邊緣 ML 對效能和功耗有著高要求,無論是傳統 CPU/GPU 或通用 ML 加速器皆無法適用於所有網路需求,特定領域架構需要新的設計方法和工具支持,且須專門開發特定數據集和應用程式,才能面向不同垂直應用的使用者經驗優化,因而吸引許多公司加入 AI/ML 行列。

由於數據爆炸,截至 2030 年,高速數據通訊將呈現指數級增長,而看似對立、卻相互影響的兩股勢力正在推進 AI:一是強化資料中心的演算能力,二是將更多處理工作推至邊緣 (Edge)。在邊緣裝置主導下,AI/ML 晶片市場將以三位數成長,力道將超越邊緣設備本身;但邊緣 ML 對效能和功耗有著高要求,無論是傳統 CPU/GPU 或通用 ML 加速器皆無法適用於所有網路需求,特定領域架構需要新的設計方法和工具支持,且須專門開發特定數據集和應用程式,才能面向不同垂直應用的使用者經驗優化,因而吸引許多公司加入 AI/ML 行列。

基本上,AI 晶片要能處理 PCIe Express 所有規格的圖形性能,亦要顧及應用程式是基於 TensorFlow 或 Caffe 學習框架編程;想達到最佳化,還得測量特定類型的應用程式數據。例如,邊緣設備的 GPU 會使用很多客製化數據中心的方法建立系統結構、進行最佳匹配,並設計能以 HLS 語言建構的演算法以便與 AI 開發環境無縫接軌——如何放置記憶體?如何管理管線 (pipeline) 及跨晶片數據?然後使用 HLS 將其自動導入邏輯閘設計。但前提是:架構效能可與應用程式必要的限制抗衡,且生態系統要夠成熟且強大。

機器學習可加速設計運算、驗證&模擬

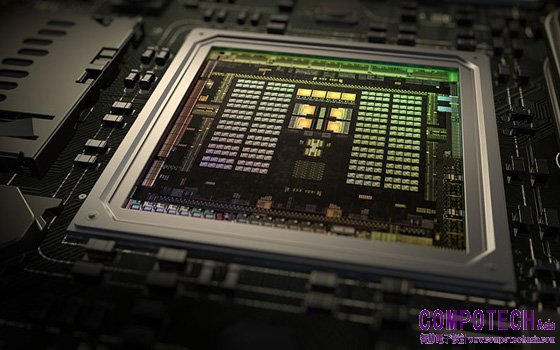

這種情況下,只要擁有一組預先建構各種神經網路設計且經過優化的智財 (IP) 就可將它們導入演示板的 FPGA 或專用晶片 (ASIC) 中,不須另行學習電子工程語言;輝達 (NVIDIA) Tegra X1 超級晶片正是借助此方,提升 50% 生產力並降低 80% 驗證成本。Sawicki 還提到,SOC 開發者多會針對正確定向的測試文本結構做數據流動的隨機測試,以確保結構和規格;有些用戶想運行一些示例數據集,有的則希望再次執行應用程式,且在矽晶片成品前對其測試。其用意在確保能獲得適合的電源類型、軟體庫已就緒,並依據 AI 引擎做調度。

這種情況下,只要擁有一組預先建構各種神經網路設計且經過優化的智財 (IP) 就可將它們導入演示板的 FPGA 或專用晶片 (ASIC) 中,不須另行學習電子工程語言;輝達 (NVIDIA) Tegra X1 超級晶片正是借助此方,提升 50% 生產力並降低 80% 驗證成本。Sawicki 還提到,SOC 開發者多會針對正確定向的測試文本結構做數據流動的隨機測試,以確保結構和規格;有些用戶想運行一些示例數據集,有的則希望再次執行應用程式,且在矽晶片成品前對其測試。其用意在確保能獲得適合的電源類型、軟體庫已就緒,並依據 AI 引擎做調度。

圖1:NVIDIA Tegra X1 基於 NVIDIA Maxwell 架構、256 個 GPU 核心、1個 64 位元 CPU,提供 4K 影片功能及更好的省電效果,適用於行動與汽車環境

將軟體調試與硬體開發環境連結,方便使用者運行軟體調試庫的各個寄存器內容,以執行實際應用程式的真正功耗、進而優化軟體堆疊。以 OPC (光學趨近校正) 光罩為例,光刻非常複雜,有些 CPU 的先進節點可能需要 24 小時才能完成所有運算,利用機器學習能加速 3~4 倍,大幅縮短處理時間及取得第一個工程樣品的時程,亦可協助解決設計中出現的產量限制因素,還能減少蒙地卡羅 (Monte Carlo) 分析或高訊號驗證等模擬量。再者,結合 EDA 工具生成測試模式更便於確認晶片結構,機器學習可獲取故障晶片的工作日誌、從中洞悉資料庫內容。

西門子+Mentor 併購綜效已現!

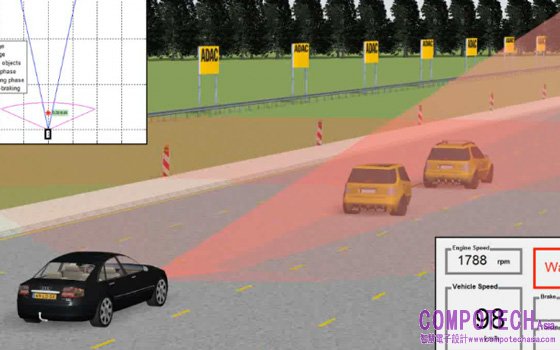

兩年前西門子收購 Mentor 後,更讓雙方在面對一階原始設備製造商 (OEM) 時,更有整合軟、硬體的本錢,中樞則是對接虛擬化介面的驗證環境。過去十年中,西門子已投資百億美元在以大型 AI 引擎建模環境上,而併購 Mentor 的綜效亦逐漸顯現——藉由西門子的電子設備收集虛擬環境的自動駕駛資訊、創建數位雙胞胎 (Digital Twins) 便是其中之一。Siemens Center PreScan 是一個虛擬工具,可用於創建道路模擬交叉路口、各種交通號誌和自行車/行人專用道等。透過為立體成像設置兩個攝影鏡頭並模擬、處理數據,可加速感測數據。

兩年前西門子收購 Mentor 後,更讓雙方在面對一階原始設備製造商 (OEM) 時,更有整合軟、硬體的本錢,中樞則是對接虛擬化介面的驗證環境。過去十年中,西門子已投資百億美元在以大型 AI 引擎建模環境上,而併購 Mentor 的綜效亦逐漸顯現——藉由西門子的電子設備收集虛擬環境的自動駕駛資訊、創建數位雙胞胎 (Digital Twins) 便是其中之一。Siemens Center PreScan 是一個虛擬工具,可用於創建道路模擬交叉路口、各種交通號誌和自行車/行人專用道等。透過為立體成像設置兩個攝影鏡頭並模擬、處理數據,可加速感測數據。

圖2:模擬歐洲 NCAP 對於無人車自動緊急煞車系統 (AEB) 的測試場景

當發生事故、欲將控制權移交給傳動系統,需先為底盤建模 (例如:煞車需要多少時間),再將其作為狀態訊息回傳從矽晶片設計定案到量產,都可在這個虛擬環境創造「數位雙胞胎」以衡量系統性能,加速開發及上市,設計涉及兩方面:一是在這些邏輯閘區域器件的表徵和寄生提取,因為這些堆疊器件的金屬下層結構之間,會存在潛在交互作用;二是確保建模的擬真度 (fidelity),這是最後階段「診斷」(Diagnostics) 工序的難點之一。要在 3D 堆疊單元內查找故障並不容易,因為它們會在堆疊的 Z 軸游移,須將這些問題橋接起來才能發現。

不只系統商!半導體對 AI 人才亦需求孔急

圍繞 C++ 系統建構須與時俱進,而將到期日納入新的語言類型以及這些語言如何影響流程亦很重要;Sawicki 認為,與小型團隊合作有助於成功服務市場,但他也感歎優秀的 AI 人才似乎都偏好投入系統商懷抱。的確,諸如臉書 (Facebook) 之類的處理、搜尋晶片經濟利益誘人;不過,EDA 廠商更關注 AI 的多樣性,著重與 IP 庫相關的 C 語言編程、而非如何驅動在 HLS 環境中工作的神經元,是一個涵蓋 3D 堆疊和系統級異質整合、不斷增長的產品組合。例如,將內建處理器接口的高頻寬 DRAM 與帶有處理元件的射頻前端 (RFFE) 集成在一起。

圍繞 C++ 系統建構須與時俱進,而將到期日納入新的語言類型以及這些語言如何影響流程亦很重要;Sawicki 認為,與小型團隊合作有助於成功服務市場,但他也感歎優秀的 AI 人才似乎都偏好投入系統商懷抱。的確,諸如臉書 (Facebook) 之類的處理、搜尋晶片經濟利益誘人;不過,EDA 廠商更關注 AI 的多樣性,著重與 IP 庫相關的 C 語言編程、而非如何驅動在 HLS 環境中工作的神經元,是一個涵蓋 3D 堆疊和系統級異質整合、不斷增長的產品組合。例如,將內建處理器接口的高頻寬 DRAM 與帶有處理元件的射頻前端 (RFFE) 集成在一起。

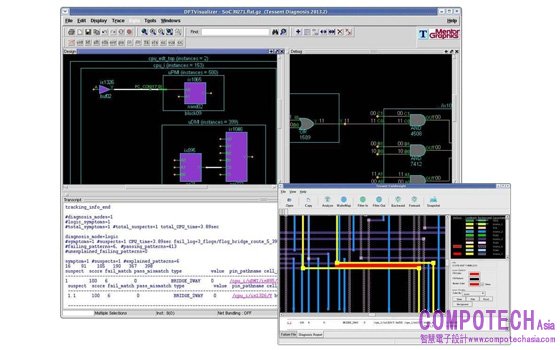

圖3:Mentor「Tessent」診斷工具具有佈局感知和單元感知能力,可準確識別缺陷的位置和分類,大幅減少故障分析的工作量,並實現診斷驅動的良率分析流程

資料來源:https://www.mentor.com/products/silicon-yield/products/diagnosis

資料來源:https://www.mentor.com/products/silicon-yield/products/diagnosis

過去五年中,Mentor 一直在研究五種組合技術,並將物理驗證工具分組以便各領域相互交流,且確保這些設計能正確組合、封裝並運行;假以時日,這將成為行業能力的大勢所趨,即使只是簡單地在電路板製圖 (Gerber) 數據庫格式與佈局、繞線後所產生的 GDS II 檔案進行轉換——Gerber 數據庫是傳統格式,而 GDS II 是關於 IC 規範的描述。此前,業界從未討論過以兩種金屬解決的工具,但這樣的新解方將在不日內出現,將對化學機械平坦化 (CMP) 加工產出帶來新挑戰;此時,EDA 工具可透過獲取輸入數據庫並模擬 CMP 作用。

如此一來,可預先掌握運行之後的表面拓樸,讓設計者得以再次進行一組虛擬處理、調整 CMP 流程特性,以獲得整體關鍵因素;落差越少,下一個堆疊級別的性能就越好。另一個則是「池」,作為 CMP 一部分,如果採用的是金屬三層、斷開晶片各部分連接,或將有很多區域透過未經製造商允許的線路穿過並循此方式製造,由此獲得的複本不會在下一層產出,因為基礎層不會發揮作用,稱為「虛擬填充」(Dummy Fill);但若得「智能填充」工具之助,可測量密度且不使任何觸點相連,僅放置在適當位置以管理設備的平坦性,能獲得更好的平坦效果。