不管經濟環境的不明朗將對 EDA 產業形成嚴峻挑戰,但不可否認的是,EDA 的重要性正逐漸由 IC 設計、製造端向軟/硬體系統及終端產品廠商擴散。另一方面,藉併購或簽署合作協議與應用處理器 IP (矽智財專利) 供應商「抱團」,不僅有助拓展市佔率,在進軍 SoC 亦更具綜效。2013 年宣布收購 Tensilica 的益華電腦 (Cadence),就得益於 Tensilica 資料平面處理單元 (Dataplane Processing Units, DPUs),在客製硬體設計達到最佳功耗、性能和面積效率,且能與業界標準的 CPU 架構協同工作。與此同時,和安謀國際 (ARM) 保持合作關係。

精細優化,高度依賴設計工具

Cadence 全球副總裁暨亞太區總裁石豐瑜表示,雖然摩爾定律終究有其極限,且全球 IC 設計產業經過不斷整併,多少對 EDA 產業造成衝擊;然隨著製程技術不斷進步,需要的工具會越來越多,對 EDA 仍有一定的支撐。石豐瑜亦看好物聯網興起將賦予 EDA 新的成長動能,認為 IoT 不是只有一個晶片就能成事,還需要強大的應用和營運為後援,這往往是系統公司的核心競爭力所在。另為了避免知識產權外洩,有越來越多的系統公司起心動念,想自行投入 IC 設計工作;若能借助 EDA 建構截然不同、別具意義的生態鏈,系統商何樂而不為?

Cadence 全球副總裁暨亞太區總裁石豐瑜表示,雖然摩爾定律終究有其極限,且全球 IC 設計產業經過不斷整併,多少對 EDA 產業造成衝擊;然隨著製程技術不斷進步,需要的工具會越來越多,對 EDA 仍有一定的支撐。石豐瑜亦看好物聯網興起將賦予 EDA 新的成長動能,認為 IoT 不是只有一個晶片就能成事,還需要強大的應用和營運為後援,這往往是系統公司的核心競爭力所在。另為了避免知識產權外洩,有越來越多的系統公司起心動念,想自行投入 IC 設計工作;若能借助 EDA 建構截然不同、別具意義的生態鏈,系統商何樂而不為?

照片人物:(左起) Cadence EDA 策略長暨資深副總裁徐季平、台灣區總經理宋栢安、全球副總裁暨亞太區總裁石豐瑜

「Cadence 相當重視研發,近兩、三年的研發投資更高達營收 35%,密集推出十二個全新或大改款的產品,使台灣技術團隊每年得以保持 25% 以上的成長」,石豐瑜強調。今年 5 月甫履新台灣區總經理的宋栢安,以自身曾在系統商工作的經驗分享,IoT 強調的低功耗、小尺寸需求在系統設計端仍有諸多問題待解,且需溯源至晶片設計及製造,無論是否採用先進製程,都將使 EDA 發展空間更寬廣。EDA 策略長暨資深副總裁徐季平從技術層面解析,上個世紀製程只關注晶片連接線越短越好,但今後的先進製程在概念上截然不同。

製程邏輯丕變,EDA 須與時俱進

7nm 以下為減少零碎浪費,已捨棄「把不要的部分去掉」之減法思維,改成先把所有佈線做好、再蝕刻成想要的樣子,作為重要輔具的 EDA 亦須與時俱進。為進一步追求晶片效能,時序與多重曝光 (multi‐patterning) 的佈局顏色類別定義須更細緻,不能粗略以臨界值合格與否帶過,正是設計優化與製程挑戰的精髓所在。Cadence Virtuoso 佈局套件擁有以下增強功能,有助解決此難題:

1. 圖形表現:可在大型佈局提供從 10~100 倍的加速縮放、平移、拖放與圖形效能表現;

2. 模組產生器 (ModGen):視覺化的互動式圖樣 (pattern) 操作流程,便於即時客製化設計、可支援同步複製,且擁有完全相同物理特性的佈局元件 (例如:電晶體的寬度與長度),可讓設計人員重複套用既有佈局;

3. 元件級 (device-level) 繞線:新式結構最高可增加 50% 的繞線生產力;

4. 整合 ADE (類比設計環境):在資料庫容量超過 1GB 時,最高可提升 20 倍的波形載入、50 倍的版本控制 (versioning) 與載入設定檔案,加快 5~10 倍的簽核 (signoff) 時序收斂速度,並顯著提升功率、效能與面積 (PPA)。

7nm 以下為減少零碎浪費,已捨棄「把不要的部分去掉」之減法思維,改成先把所有佈線做好、再蝕刻成想要的樣子,作為重要輔具的 EDA 亦須與時俱進。為進一步追求晶片效能,時序與多重曝光 (multi‐patterning) 的佈局顏色類別定義須更細緻,不能粗略以臨界值合格與否帶過,正是設計優化與製程挑戰的精髓所在。Cadence Virtuoso 佈局套件擁有以下增強功能,有助解決此難題:

1. 圖形表現:可在大型佈局提供從 10~100 倍的加速縮放、平移、拖放與圖形效能表現;

2. 模組產生器 (ModGen):視覺化的互動式圖樣 (pattern) 操作流程,便於即時客製化設計、可支援同步複製,且擁有完全相同物理特性的佈局元件 (例如:電晶體的寬度與長度),可讓設計人員重複套用既有佈局;

3. 元件級 (device-level) 繞線:新式結構最高可增加 50% 的繞線生產力;

4. 整合 ADE (類比設計環境):在資料庫容量超過 1GB 時,最高可提升 20 倍的波形載入、50 倍的版本控制 (versioning) 與載入設定檔案,加快 5~10 倍的簽核 (signoff) 時序收斂速度,並顯著提升功率、效能與面積 (PPA)。

表:Cadence Virtuoso ADE (類比設計環境) 三大核心技術

|

類型 |

說明 |

|

|

Virtuoso ADE Explorer |

實現快速、準確的設計規格即時調整,提供合格/失敗的資料表,以及完整的 Corner 與 Monte Carlo 統計環境,以偵測和修補變異性問題。 |

|

|

Virtuoso ADE Assembler |

協助工程師在不同的製程—-電壓—溫度 (PVT) 組合條件下分析其設計,並提供基於 GUI 的驗證計畫,可輕鬆建立條件與相依性模擬。 |

|

|

Virtuoso ADE Verifier |

為類比驗證提供顯著的技術進展,提供整合式儀表板,可讓工程師輕鬆驗證與整體設計規格有關的所有模組。 |

|

Cadence 對於「混合訊號設計的動態模擬」尤為擅長,其 Virtuoso Liberate AMS 特性分析可較傳統 FastSPICE 模擬方法提升 20 倍的速度分析擁有數百萬相關寄生元素的混合訊號巨集之「佈局後網表」(post-layout netlists) 特性,並保有真正 SPICE 電路模擬精準度,實現準確 SoC 簽核。隨著 SoC 複雜度日增,無論重複利用 IP 或靜態分析皆須為執行 digital-on-top 設計流程簽核;為簡化流程,Virtuoso Liberate AMS 掌握數位與類比路徑互動,並在最終 Liberty 庫建立模型,使大型混合訊號巨集區塊的標準 Liberty 模型建立工作自動化。

混合訊號設計竅門:動態模擬、設計簽核、自動建立模型、硬體驗證

這套適用於鎖相迴路 (PLLs)、資料轉換、高速收發器與 I/O 等混合訊號區塊的動態模擬工具,能為大型混合訊號巨集區塊自動建立 Liberty 模型,深受 IC 設計業者所讚許:「基本上,有能力且願意幫我們建構混合訊號測試模型的廠商少之又少」,他們強調。此外,Virtuoso Liberate AMS 以獨特的混合式電路行為切割,以及將定義的電路邏輯描繪出混合訊號電路區塊特性,可提高生產力、縮短周轉時間,並整合於 Cadence Virtuoso 類比設計環境 XL 平台模擬訊號設定,將模擬結果納入 liberty 模型 (.lib file),對客製化晶片設計助益甚大。

這套適用於鎖相迴路 (PLLs)、資料轉換、高速收發器與 I/O 等混合訊號區塊的動態模擬工具,能為大型混合訊號巨集區塊自動建立 Liberty 模型,深受 IC 設計業者所讚許:「基本上,有能力且願意幫我們建構混合訊號測試模型的廠商少之又少」,他們強調。此外,Virtuoso Liberate AMS 以獨特的混合式電路行為切割,以及將定義的電路邏輯描繪出混合訊號電路區塊特性,可提高生產力、縮短周轉時間,並整合於 Cadence Virtuoso 類比設計環境 XL 平台模擬訊號設定,將模擬結果納入 liberty 模型 (.lib file),對客製化晶片設計助益甚大。

在硬體驗證方面,Palladium Z1 平台可提供獨特的虛擬目標重新分配 (relocation) 功能,並能在執行期間將有效負載配置至可用資源,避免重新編譯 (re-compiles)。運用巨量平行處理器架構,Palladium Z1 分配精細度 (granularity) 可提高四倍,可同時「迎戰」來自數十個不同設計專案、以及數千個規模各異的驗證負載需求,適用於數百萬至數十億個邏輯閘設計,能在緊湊的開發時程確保系統功能性,是系統開發套件的重要支柱之一;設計團隊能將硬體模擬作為資料中心的運算資源,一如軟體模擬所用的刀鋒伺服器運算中心。

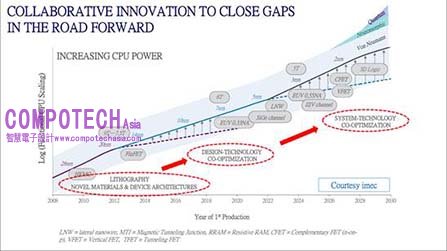

圖1:Cadence 主張合作創新,有助於縮減新材料及結構蝕刻 (lithography) 以及設計和系統優化的隔閡

資料來源:Cadence

時序簽核,加快設計收斂並優化 PPA 成果

Cadence 近期推出用於 Cortex-A73 中央處理器 (CPU) 及 Mali-G71 繪圖處理器 (GPU) 內部流程設計的快速採用套件 (RAK),即是運用 Cadence 數位實現與 Tempus 時序簽核工具開發 10nm 製程,為 RAK 提供軟體技術及製程設計套件 (PDK) 更新,加快設計收斂並優化 PPA 成果,提升行動裝置的虛擬實境 (VR) 及擴增實境 (AR) 體驗。針對訴求安全及節能的物聯網 (IoT) 應用,亦有 Cortex-M23 及 Cortex-M33 CPU 專用 RAK;透過 IEEE 1801 標準規範的「多模多角」(multi-mode, multi-corner) RTL 至 GDS 流程,達到前述目標。

Cadence 近期推出用於 Cortex-A73 中央處理器 (CPU) 及 Mali-G71 繪圖處理器 (GPU) 內部流程設計的快速採用套件 (RAK),即是運用 Cadence 數位實現與 Tempus 時序簽核工具開發 10nm 製程,為 RAK 提供軟體技術及製程設計套件 (PDK) 更新,加快設計收斂並優化 PPA 成果,提升行動裝置的虛擬實境 (VR) 及擴增實境 (AR) 體驗。針對訴求安全及節能的物聯網 (IoT) 應用,亦有 Cortex-M23 及 Cortex-M33 CPU 專用 RAK;透過 IEEE 1801 標準規範的「多模多角」(multi-mode, multi-corner) RTL 至 GDS 流程,達到前述目標。

Tempus 時序簽核為一款通過矽晶驗證之精確、色彩意識時序簽核與訊號完整性的分析工具,可支援波形傳播、米勒效應、超低功耗以及與多重曝光技術相關變異等的先進節點設計需求;它具備大量平行化運算與「實體意識時序最佳化」能力,方便設計人員大幅減少工程變更指令 (ECO) 設計往返,縮短簽核收斂時間;客戶亦可運用多執行緒及可分配路徑分析 (PBA) 能力,在數分鐘內分析設計中之上千條重要路徑;而非像傳統靜態時序分析方法,只會一股腦兒列出數百筆的違規錯誤,卻難以察覺其間關聯性,毫無頭緒可言。

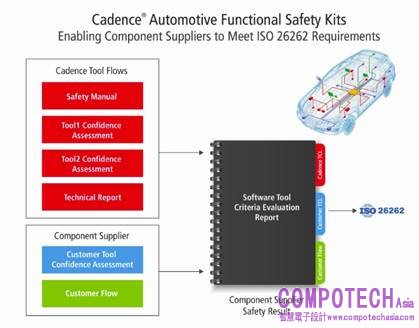

進軍車用,瞄準 ISO 26262

特別一提的是,因應汽車元件供應商的開發工具必須通過 ISO 26262 標準才能取得車輛安全完整性等級 (ASIL) 的需求,Cadence 宣佈率先推出符合 ISO 26262 標準的全面性一級軟體工具信賴水準 (TCL1) 文件,且經國際公認獨立測試與合規評估公司TÜV SÜD完成評估及確認;Cadence 並預告,數位實現與簽核流程的評估也可望於年底前完成。待其完成後,將有超過 30 種 Cadence EDA 工具可用於車用類比/混合訊號工具鏈,以及數位前端設計與驗證流程的高規格,為汽車產業的開發生命週期提供全面

特別一提的是,因應汽車元件供應商的開發工具必須通過 ISO 26262 標準才能取得車輛安全完整性等級 (ASIL) 的需求,Cadence 宣佈率先推出符合 ISO 26262 標準的全面性一級軟體工具信賴水準 (TCL1) 文件,且經國際公認獨立測試與合規評估公司TÜV SÜD完成評估及確認;Cadence 並預告,數位實現與簽核流程的評估也可望於年底前完成。待其完成後,將有超過 30 種 Cadence EDA 工具可用於車用類比/混合訊號工具鏈,以及數位前端設計與驗證流程的高規格,為汽車產業的開發生命週期提供全面

工具支援。

圖2:Cadence「汽車功能安全套件」工具流程符合規範,用戶能據以創建並驗證汽車設計

資料來源:Cadence 提供

TCL1 代表「對於工具使用安全的高信心水準」,協助汽車 OEM 廠和第一、二級零組件供應商能符合 ASIL A 到 ASIL D 的嚴格安全要求。Cadence 汽車功能安全套件提供「模組化文件」的流程式解決方案,讓用戶可依特定工具環境進行調整,便於提交文件程序:

1. 數位前端設計與驗證:從規格到 RTL 設計、功能驗證及功能安全;

2. 類比/混合訊號設計、實現與驗證:運用 Cadence Virtuoso 套件及 Spectre 電路模擬平台,經由實體實現與驗證,支援電晶體級設計的創建與模擬,以確認安全規格與個別電路規格是否相符;

1. 數位前端設計與驗證:從規格到 RTL 設計、功能驗證及功能安全;

2. 類比/混合訊號設計、實現與驗證:運用 Cadence Virtuoso 套件及 Spectre 電路模擬平台,經由實體實現與驗證,支援電晶體級設計的創建與模擬,以確認安全規格與個別電路規格是否相符;

3. 數位設計實現與簽核:目前尚在評估階段,涵蓋 RTL 至 GDSII 設計實現與簽核,包括專用於汽車設計實現與簽核的 Cadence Innovus 設計實現系統和 Modus 測試方案。

RTL 意指「暫存器轉換階層」(Register Transfer Level),是一種較系統層級更低階的電路描述方式,大量使用暫存器與算數邏輯元件來描述電路,好處是:只須以 VHDL、Verilog 或 SystemC 等基礎程式語言,就能將軟體設計導入模組、轉化成實體的晶片。如此一來,可減少設計專案評估心力、避免工具資格確認過程耗用過高成本並降低複雜度;而 Cadence「汽車功能安全套件」已經 TÜV SÜD 認可,備有完整 TCL 預先確定程序文件,能滿足供應商必須就工具及流程所提供文件的要求,並已獲車用微控制器 (MCU) 大廠——英飛凌 (Infineon) 肯定。